|

MPC8xx系列处理器的嵌入式系统电源设计

Motorola公司的PowerPC嵌入式处理器在全球通信处理器市场上处于无可争议的领先地位(占据70%以上的市场份额),这主要应当归功于PowerQUICC系列的PowerPC嵌入式处理器芯片,即MPC8xx系列处理器(包括MPC823、MPC850、MPC855、MPC860等)。

MPC8xx系列嵌入式处理器电源模块的结构和特性与其它类型的嵌入式处理器有较大差异,与微控制器(MCU)和数字信号处理器(DSP)差别更大。正确了解和理解其结构和特点,对于其外部电源电路设计是非常重要的。因此,首先介绍电源模块的功能框图和电源引唧,然后在此基础上说明电源电路的设计方法和实用电路。

1 MPc8xx系列处理器电源系统

为了保证电池供电系统的电池寿命,MPC8xx系列处理器的电源系统提供了5种类型的节电模式:正常模式(包括正常高和正常低2个模式)、磕睡模式、睡眠模式、深度睡眠模式和下电模式。为此,MPC8xx系列处理器设计了如图1所示的电源系统结构,其电源引脚描述如表l所列。

由图1可知,MPC8xx处理器内置有4种不同的电源平面,通常称之为供电轨道。系统设计者可以为每一种供电轨道提供一种电源。其中,I/O缓冲器、系统锁相环(SPLL―System Phase―Locked Loop)的数字部分和时钟控制部分电路是由VDDH引脚提供的3.3V±5%电源供电的,在此称之为VDDH供电轨道;内部逻辑(包括PowerPC嵌入式处理器模块、通信处理器模块和系统接口单元等的逻辑电路)和时钟驱动是由VDDL引脚提供的3.3V电源供电,在此称之为VDDL,供电轨道;为了提高系统时钟信号(CLKOUT)的稳定性,SPLL模拟部分需要一个独立的3.3V供电电源,其由VDDSYN引脚提供,在此称之为VDDSYN供电轨道;主振荡器模块(OSCM)、时基计数器(TB―Timebase Counter)、递减器(DEC―Derementer)、周期中断定时器(PIT―Periodic Interrupt Timer)、实时时钟(RTC―Real-Time Clock)、系统时钟与复位控制寄存器(SCCR―System Clock and Reset Control Register)、锁相环低功耗与复位控制寄存器(PLPRCR―PLL,Low―Power and Reset Control Register)和复位状态寄存器(RSR―Reset Status Register)是由保持有效电源(KAPWR―Keep―alive-Power)引脚提供的电源供电的,在此称之为KAPWR供电轨道。这种体系结构的供电方式允许设计者在睡眠、深度睡眠或下电模式期间,关闭VDDH、VDDL和VDDSYN引脚的电源。设计者可以使用定时器溢出输出的TEXP引脚信号控制外部供电电路,在关闭上述3种电源后,保持KAPWR供电轨道的电源,从而最大限度地提高电池的寿命。

当MPC8xx处理器处在正常工作模式(包括正常高和正常低工作模式)时,其内部绝大部分电路的电源是自正常供电引脚一VDDH、VDDL和VSS提供的,采用这样供电方案的目的是在系统空闲时降低其功耗。但是,需要注意的是,正常工作模式的各供电轨道对电源电压的要求。由图1可知,在正常工作模式时,通常要求VDDH的电源电压大干或等于VDDL的电源电压;VDDH电源电压大于KAPWR电源电压。由于KAPWR通常是由外部带有后备电池供电电路提供的,因此需要在供电电路中加入正常工作电压与后备电池之间的切换电路,这样就使得对KAPWR供电电压要有一定程度的降低。通常,若VDDH和VDDL供电电压为3.3V,则KAPWR2.9V~3.3V。

MPC8xx处理器的系统配置与保护模块寄存器(包括PIT、RTC、TB和DEC)和系统时钟、电源和复位控制寄存器(包括SCCR、PLPRCR和RSR)是由KAPWR供电的,这些寄存器都有与其关联的写保护寄存器,通常称之为钥匙寄存器。当MPC8xx处理器进入下电模式之后,系统主电源(VDDH和VDDL)被断开,这些寄存器值就被自动保护起来。若在主电源断开之前,不进入下电模式,则会丢失数据。因此,为了保护系统的关键数据,通过写与其关联的钥匙寄存器来锁定由KAPWR供电的寄存器。一旦锁定了一个寄存器,就不能对其进行写操作,若要试图进行写,则会产生一个检错中断。在KAPR供电轨道区域内的每个寄存器都有一个可以处于打开或锁定状态的钥匙寄存器。在上电复位时,除了实时时钟钥匙寄存器外,所有钥匙寄存器都被打开。每个钥匙寄存器在内部存储器图中都有一个与其关联的地址,若写0x55CCAA33到任何一个钥匙寄存器,则与此钥匙寄存器对应的寄存器就被打开,此时此寄存器就可以访问了;若写其它值,则其将被锁定。例如,写Ox55CCAA33到钥匙寄存器RTCK,则将允许用户访问RTC寄存器。

MPC8xx处理器除了采用上述的节电方案外,在通信处理器模块(CPM)中还设计了自己的节电机制逻辑电路,当CPM空闲时,此逻辑电路就自动关闭其时钟。

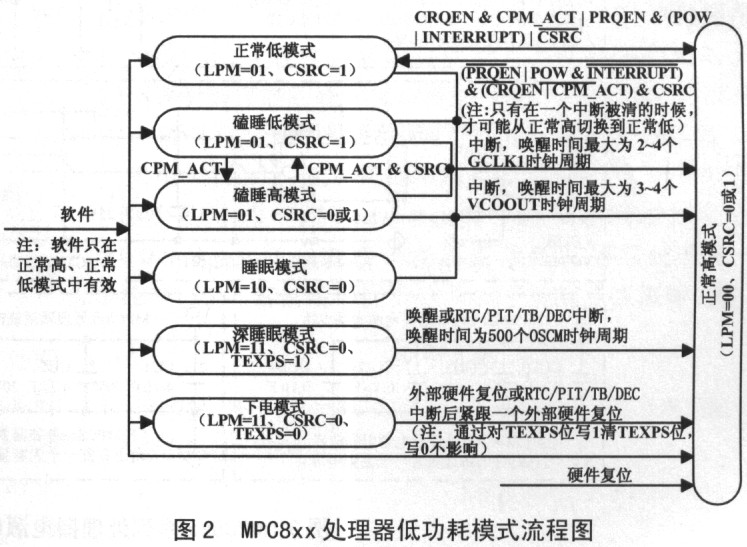

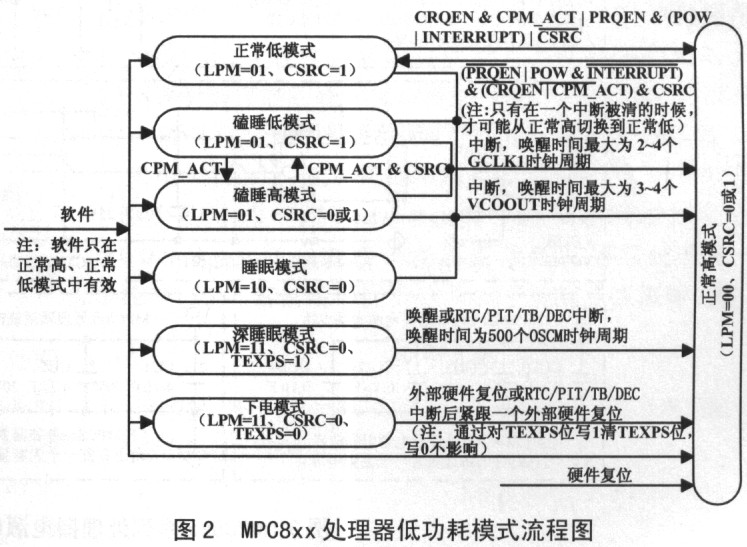

2 MPC8xx处理器各种功耗模式之间的切换

MPC8xx处理器低功耗模式操作是受时钟模块中低功耗分频器控制的。此低功耗分频器允许用户在保持SPLL锁定的状态下,动态地调整MPC8xx处理器各模块操作频率。在正常低模式中,用户可以在非常低的频率下保持整个芯片的功能。当时钟分频器值被修改时,立即改变系统操作频率。通过修改SCCR中的分频系数字段的数值,就可以控制低功耗分频器。通过软件正确设置PLPRCR中的系统时钟源(CSRC)和低功耗模式(LPM)字段,以及机器状态寄存器(hISR―Machine Status Register)中的POW位,MPC。8xx处理器就可以从正常模式进入磕睡、睡眠或下电模式,并且其使用中断(包括来自中断控制器的唤醒中断一jrqx信号和来自系统配置和保护逻辑的RTC、PIT、TB或DEC中断)自动退出上述低功耗模式,如图2所示。注意一个使能中断清LPM字段,但不改变CSRC位。

来自中断控制器的唤醒中断,不是系统退出低功耗模式的快速响应中断。通常,由IRQX信号产生的中断从正常低、磕睡高、磕睡低、睡眠或深度睡眠模式唤醒的时间为3~4个SPLL输出时钟(VCOOUT)。例如,在一个75MHZ的系统中,其唤醒时间需要6Ons~8Ons。在MPC8xx系列处理器中,唤醒中断定义为来自中断控制器的电平敏感中断,其只在中断源位被清之后才无效。来自中断控制器的所有中断源唤醒时间都是使用实际运行的MPc8xx处理器的通用系统时钟(GCLKl)来测量的,一旦一个中断被识别,其将花费2~4个GcLKl时钟周期来达到正常高模式。例如,在一个75MHz、DFNL=111(256分频)的系统中,其唤醒时间为1O.24 u s~2O.48 μs。此外,来自系统配置与保护逻辑模块的实时时钟、周期中断定时器、时基计数器或递减器中的任何一个中断都可能设置PLPRCR中的定时器中断状态(TMIST)位。当TMIST位被置时,MPCC8xx处理器时钟模块把此中断作为一个待决中断,因此这种类型中断通常为快速响应唤醒中断。因此,在系统进入任何一个低功耗模式(正常高模式除外)时,必须清TMIST位。

在正常和磕睡模式中,系统可能处于由SCCR中DFNH字段定义的高模式或由DFNL字段定义的低模式,通过PLPRCR中系统时钟源(CSRC)位的设置,系统可以在高频与低频之间来回切换。在系统从正常低模式到正常高模式之前,必须满足下列条件之一:①通信处理器模块(CPM)必须有效,即CPM_ACT必须为l;②中断控制器的一个待决中断必须被识别,即INTERRUPT必须为l;③MSR中的POW位必须被清(正常模式)。若没有一个条件被满足,CSRC位被置位和中断状态被复位,则系统自动切换回正常低模式;若CPM有效,则系统自动从磕睡低模式切换到磕睡高模式,换句话说,当CPM为空闲并且CSRC为被置位,则系统自动切换回磕睡低漠式。来自中断控制器的一个待决中断把系统从磕睡模式转换为正常高模式。在复位之后和当退出低功耗模式出现复位时的缺省状态时,MPC8xx处理器都处于正常高模式。

当来自中断控制器、实时时钟、周期中断定时器、时基计数器或递减器的唤醒中断被识别时,MPC8xx处理器退出深度睡眠模式,进人正常高模式。在深度睡眠模式中,由于SPLL不使能,因此这一模式的唤醒时间最大为500个OSCM时钟。在1对1模式中,唤醒时间可能最大为1000个EXTCLK时钟。例如,若SPLL输入频率为32kHz,则唤醒时间最大为15.6ms,在1对1模式中,若SPLL输入频率为4MHz,则唤醒时间最大为125μs。

为了退出下电模式并且进入正常高模式,当定时器溢出(TEXP)引脚有效时,必须通过外部逻辑使硬件复位(HRESET)引脚有效。当来自实时时钟、周期中断定时器、时基计数器或递减器的唤醒中断出现时,自动置PLPRCR中的TEXPS位,进而使反映TEXPS位逻辑值的TEXP引脚有效。HRESET有效的时间必须比唤醒供电所花的时间与SPLL达到锁定状态所花的时间要长。退出下电模式的另一种方式是,当TEXPS位被清和TEXP引脚无效时,使HRESET引脚有效,这将导致MPC8xx处理器在复位时自动置TEXPS位,进而使TEXP引脚有效,系统进入正常高模式。通常,若定时器溢出置TEXPS位,则MPC8xx自动使TEXP引脚有效(若使能)后出现CLKOUT,表明MPC8xx正准备退出下电模式。因此,在具有下电模式功能的嵌入式系统中,必须引脚控制的电源开关电路,这样才能保证电模式时功耗达到最低。

3 MPC8xx系列处理器电源电路设计

MPC8xx系列处理器电源系统有4种类型的供电引脚:I/O缓冲器与部分时钟电路供电引脚(VDDH和GND)、内部逻辑与时钟驱动器供电引(VDDL和GND)、SPLL模拟电路供电引脚(vDDsYN和VSSSYN)、保持有效电源供电引脚(KAPWR),以及用于控制下电模式切换的电源开启与关闭定时器溢出信号引脚(TEXP),电源引脚的描述见表1。MPC8xx系列处理器电源电路设计的典型范例之一如图3所示。

由于MPC8XX处理器系统性能在很大程度上取决于时钟电路的稳定性和可靠性,而时钟电路的稳定性主要取决于系统锁相环(SPLL)的稳定性。因此,在SPLL模拟部分供电电源采用LC滤波电路,以保证供电的稳定性。保持有效电源(KAPWR)引脚为处理器内部时钟、电源和复位控制关键部件(包括OSCM、SCCR、PLPRCR、RSR、PIT、RTC、TB和DEC等)供电,这些关键部件参数对系统各种运行方式起着重要,甚至决定性的作用。因此,为了保证在各种运行方式下所设置的参数不变,通常在嵌入式系统设计中,为KAPWR提供带有后备电池的供电电路。在图3中,采用了Dallas公司的带有锂电池监视器的3V非易失性控制器DSl314作为VCC与后备电池的自动切换开关。在嵌入式系统设计中,设计者可以利月DSl314的BW引脚来监视电池的状况。系统的主电源采用一个5.OV输入/3.3V输出的电压调整器(RAG-3V)作为主器件,其不仅为VDDH和VDDL供电轨道提供电源,而且还为整个系统提供5.OV和3.3V电源。在图3中,还给出了MPC8xx嵌入式系统电源去耦和机壳地等PCB设计方法。在PCB设计时,尽量采用图3中建议的布局和布线方法,以便最大限度地保证供电系统的稳定性和可靠性。此外,在系统设计中,每个集成电路器件的电源端应该尽可能加接一个O.1 μF的无极性去耦电容,并且要求此电容引脚尽可能靠近器件的电源引脚,这种方法已经成为嵌入式系统保持集成电路器供电稳定性的一种常规方法。

图3给出的供电电路是一种比较典型的MPC8xx处理器供电系统实用电路,其可以满足大部分的MPC8xx嵌入式系统的设计要求,但是此供电系统设计有一个缺陷,即没有考虑下电模式的电源控制问题。因此,对于采用电池供电的MPC8xx嵌入式系统来讲,此电路还需要采用图4的方法进行改进。

在此电路中,增加了下电模式控制电路。当系统从正常模式进入下电模式(LPM=11,TEXPS=0)时,TEXP引脚输出低电平使电源开关U3(为处理器提供电源)和U5(为系统中其他电路提供电源)输出关闭;当来自实时时钟、周期中断定时器、时基计数器、递减器的唤醒中断或系统复位时,由于PLPRCR中的TEXPS位自动被置,因此TEXP引脚输出高电平使电源开关U3和U5输出打开,系统退出下电模式进入正常高模式。由于在退出下电模式进入正常高模式时.要求当TEXP有效时硬件复位(HRESET)信号必须同时有效,因此电路中增加了由TEXP引脚控制的硬件复位电路(U4)。当TEXP由低变高时,硬件复位电路使而HRESET有效。此电路中,电源开关采用Micrel公司的单通电源开关芯片一MIC2025/75(最大的导通电阻为14OmΩ最小连续输出电流为500mA);复位电路采用双可重触发的复位芯片―74Ll23,其常用于作为嵌入式系统的复位器件。

| 会员服务热线: |

深圳矽通科技版权所有 © Copyright 2005-2007, ic-cn.com.cn All Right Reserved. |

|

深 圳:13410210660 QQ : 317143513  |

|

客服联系: MSN:CaiZH01@hotmail.com E-mail:CaiZH01@163.com |

|

|